Full text available at: http://dx.doi.org/10.1561/100000008

Statistical Performance Modeling and Optimization

# Statistical Performance Modeling and Optimization

### Xin Li

Carnegie Mellon University Pittsburgh, PA 15213, USA xinli@ece.cmu.edu

### Jiayong Le

Extreme DA Palo Alto, CA 94301, USA kelvin@extreme-da.com

### Lawrence T. Pileggi

Carnegie Mellon University Pittsburgh, PA 15213, USA pileggi@ece.cmu.edu

Boston – Delft

## Foundations and Trends<sup>®</sup> in Electronic Design Automation

Published, sold and distributed by: now Publishers Inc. PO Box 1024 Hanover, MA 02339 USA Tel. +1-781-985-4510 www.nowpublishers.com sales@nowpublishers.com

Outside North America: now Publishers Inc. PO Box 179 2600 AD Delft The Netherlands Tel. +31-6-51115274

The preferred citation for this publication is X. Li, J. Le and L. T. Pileggi, Statistical Performance Modeling and Optimization, Foundations and Trends<sup>®</sup> in Electronic Design Automation, vol 1, no 4, pp 331–480, 2006

ISBN: 978-1-60198-056-4 © 2007 X. Li, J. Le and L. T. Pileggi

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, mechanical, photocopying, recording or otherwise, without prior written permission of the publishers.

Photocopying. In the USA: This journal is registered at the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923. Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by now Publishers Inc for users registered with the Copyright Clearance Center (CCC). The 'services' for users can be found on the internet at: www.copyright.com

For those organizations that have been granted a photocopy license, a separate system of payment has been arranged. Authorization does not extend to other kinds of copying, such as that for general distribution, for advertising or promotional purposes, for creating new collective works, or for resale. In the rest of the world: Permission to photocopy must be obtained from the copyright owner. Please apply to now Publishers Inc., PO Box 1024, Hanover, MA 02339, USA; Tel. +1-781-871-0245; www.nowpublishers.com; sales@nowpublishers.com

now Publishers Inc. has an exclusive license to publish this material worldwide. Permission to use this content must be obtained from the copyright license holder. Please apply to now Publishers, PO Box 179, 2600 AD Delft, The Netherlands, www.nowpublishers.com; e-mail: sales@nowpublishers.com

### Foundations and Trends<sup>®</sup> in Electronic Design Automation Volume 1 Issue 4, 2006 Editorial Board

### Editor-in-Chief:

Sharad Malik Department of Electrical Engineering Princeton University Princeton, NJ 08544

#### Editors

Robert K. Brayton (UC Berkeley) Raul Camposano (Synopsys) K.T. Tim Cheng (UC Santa Barbara) Jason Cong (UCLA) Masahiro Fujita (University of Tokyo) Georges Gielen (KU Leuven) Tom Henzinger (EPFL) Andrew Kahng (UC San Diego) Andreas Kuehlmann (Cadence Berkeley Labs) Ralph Otten (TU Eindhoven) Joel Phillips (Cadence Berkeley Labs) Jonathan Rose (University of Toronto) Rob Rutenbar (CMU) Alberto Sangiovanni-Vincentelli (UC Berkeley) Leon Stok (IBM Research)

### **Editorial Scope**

Foundations and Trends<sup>®</sup> in Electronic Design Automation will publish survey and tutorial articles in the following topics:

- System Level Design

- Behavioral Synthesis

- Logic Design

- Verification

- Test

- Physical Design

- Circuit Level Design

- Reconfigurable Systems

- Analog Design

#### Information for Librarians

Foundations and Trends<sup>®</sup> in Electronic Design Automation, 2006, Volume 1, 4 issues. ISSN paper version 1551-3939. ISSN online version 1551-3947. Also available as a combined paper and online subscription.

Foundations and Trends<sup>(f)</sup> in Electronic Design Automation Vol. 1, No. 4 (2006) 331–480 (© 2007 X. Li, J. Le and L. T. Pileggi DOI: 10.1561/100000008

### Statistical Performance Modeling and Optimization

### Xin $Li^1$ , Jiayong $Le^2$ and Lawrence T. Pileggi<sup>3</sup>

- <sup>1</sup> Department of ECE, Carnegie Mellon University, Pittsburgh, PA 15213, USA, xinli@ece.cmu.edu

- <sup>2</sup> Extreme DA, 165 University Avenue, Palo Alto, CA 94301, USA, kelvin@extreme-da.com

- <sup>3</sup> Department of ECE, Carnegie Mellon University, Pittsburgh, PA 15213, USA, pileggi@ece.cmu.edu

#### Abstract

As IC technologies scale to finer feature sizes, it becomes increasingly difficult to control the relative process variations. The increasing fluctuations in manufacturing processes have introduced unavoidable and significant uncertainty in circuit performance; hence ensuring manufacturability has been identified as one of the top priorities of today's IC design problems. In this paper, we review various statistical methodologies that have been recently developed to model, analyze, and optimize performance variations at both transistor level and system level. The following topics will be discussed in detail: sources of process variations, variation characterization and modeling, Monte Carlo analysis, response surface modeling, statistical timing and leakage analysis, probability distribution extraction, parametric yield estimation and robust IC optimization. These techniques provide the necessary CAD infrastructure that facilitates the bold move from deterministic, corner-based IC design toward statistical and probabilistic design.

### Contents

| 1 ]                                      | Introduction                               | 1   |

|------------------------------------------|--------------------------------------------|-----|

| 0 1                                      |                                            | -   |

| 2 ]                                      | Process Variations                         | 5   |

| 2.1                                      | Front-End of Line (FEOL) Variations        | 5   |

| 2.2                                      | Back-End of Line (BEOL) Variations         | 9   |

| 2.3                                      | Variation Characterization                 | 11  |

| 2.4                                      | Variation Modeling                         | 14  |

| 2.5                                      | Manufacturing Yield                        | 25  |

| 3 7                                      | Transistor-Level Statistical Methodologies | 27  |

| 3.1                                      | Monte Carlo Analysis                       | 28  |

| 3.2                                      | Statistical Performance Modeling           | 37  |

| 3.3                                      | Statistical Performance Analysis           | 53  |

| 3.4                                      | Statistical Transistor-Level Optimization  | 78  |

| 4 System-Level Statistical Methodologies |                                            | 95  |

| 4.1                                      | Statistical Timing Analysis                | 96  |

| 4.2                                      | Statistical Timing Sensitivity Analysis    | 111 |

| 4.3                                      | Statistical Timing Criticality             | 123 |

| 4.4                                      | Statistical Leakage Analysis               | 125 |

### Full text available at: http://dx.doi.org/10.1561/100000008

| 5 Robust Design of Future ICs | 137 |

|-------------------------------|-----|

| Acknowledgments               | 141 |

| References                    | 143 |

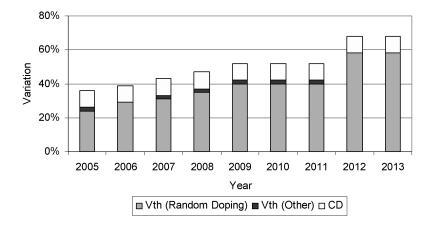

As integrated circuit (IC) technologies continue shrinking to nanoscale, there is increasing uncertainty in manufacturing process which makes it continually more challenging to create a reliable, robust design that will work properly under all manufacturing fluctuations. Large-scale process variations have already become critical and can significantly impact circuit performance even for today's technologies [14, 72, 73, 100]. Figure 1.1 shows the relative process variations ( $3\sigma$ /mean) predicted by the International Technology Roadmap for Semiconductors (ITRS) [100]. These large-scale variations introduce numerous uncertainties in circuit behavior and make it more difficult than ever to achieve a robust IC design.

In addition, when we consider some of the promising new device structures (e.g., carbon nano-tube [8, 34], FinFET [20], etc.) that have been recently proposed to maintain the aggressive pace of IC technology scaling, it is apparent that applying them to high-volume production will be a challenging problem due to the manufacturing uncertainty, or even their likelihood of failure. While it has already become extremely difficult to reliably manufacture nano-scale devices and achieve high product *yield* (defined as the proportion of the manufactured chips

Fig. 1.1 Relative process variations  $(3\sigma/\text{mean})$  predicted by [100].

that function correctly) with today's technologies, it would be almost impossible to do so affordably with tomorrow's technologies using existing deterministic design methodologies. For this reason, a paradigm shift in IC design is required to simultaneously improve circuit performance and product yield when using manufacturing technologies that present significant uncertainty.

The yield loss in a manufacturing process can be classified into two broad categories: *catastrophic* (due to physical and structural defects, e.g., open, short, etc.) and *parametric* (due to parametric variations in process parameters, e.g.,  $V_{\rm TH}$ ,  $T_{\rm OX}$ , etc.). As process variations become relatively large due to technology scaling, parametric yield loss is becoming increasingly significant at 90 nm technologies and beyond. Therefore, we focus on the parametric yield problem in this paper. We will review a number of recently-developed techniques that handle large-scale process variations at both transistor and system levels to facilitate affordable statistical integrated circuit design. Especially, we will focus on the following two questions:

• When should process variations be considered? Ideally, we want to take into account process variations in the earliest design stage. However, this strategy may not be necessary and/or efficient in practice. During early-stage system-level

design, many simplified models must be used to make the large-scale design problem tractable. The errors of these system-level models may be comparable to, or even larger than, the uncertainties caused by process variations. In such cases, it is not meaningful to model and analyze process variations at system level. As the design moves from system level down to circuit level, more accurate circuit-level models become available. We should start to consider process variations at the stage where circuit models are sufficiently accurate and process variations become the dominant uncertainties that impact performance.

• *How should process variations be considered?* For example, the simplest way to model process variations is to define a number of process corners. That is, every process parameter is assigned with a lower bound and an upper bound, and the best-case and worst-case circuit performances are computed by enumerating all possible combinations of the extreme values of process parameters. The aforementioned corner model is simple; however, such a corner-based approach may result in large error, since it completely ignores the correlation among different process parameters. In addition, it is not guaranteed that the best/worst-case performance always occurs at one of these corners. An alternative approach to model process variations is to use statistical device models where process parameters are modeled as random variables. (More details on statistical device models can be found in Chapter 2.) The statistical device model is much more accurate, but also expensive, than the traditional corner model.

One of the major objectives of this paper is to review and compare different statistical IC analysis and optimization techniques, and analyze their trade-offs for practical industrial applications. The following topics will be covered in this paper:

• Sources of process variations and their models. We will briefly review both front-end of line (FEOL) variations and back-end of line (BEOL) variations in Chapter 2. Several

3

#### 4 Introduction

techniques for variation characterization and modeling will be presented for both device-level and chip-level applications.

- Transistor-level statistical methodologies. In Chapter 3, we will discuss and compare a number of transistorlevel statistical modeling, analysis and optimization techniques. In particular, the following topics will be covered: Monte Carlo analysis, response surface modeling, probability distribution extraction, parametric yield estimation, and robust transistor-level optimization. Several recentlydeveloped methodologies, including projection-based performance modeling (PROBE) and asymptotic probability extraction (APEX), will be described in detail.

- System-level statistical methodologies. Most system-level statistical analysis and optimization techniques utilize a hierarchical flow to partition the entire system into multiple small blocks such that the large-size problem becomes tractable. In Chapter 4, we will discuss a number of system-level statistical methodologies that have been recently proposed. In particular, we will focus on the statistical timing and leakage problems for large-scale digital systems.

Finally, we will conclude and propose several possible areas for future research in Chapter 5.

- H. Abdel-Malek and A. Hassan, "The ellipsoidal technique for design centering and region approximation," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 10, no. 8, pp. 1006–1014, August 1991.

- [2] A. Agarwal, D. Blaauw, and V. Zolotov, "Statistical timing analysis for intradie process variations with spatial correlations," in *IEEE International Conference on Computer Aided Design*, pp. 900–907, 2003.

- [3] A. Agarwal, V. Zolotov, and D. Blaauw, "Statistical timing analysis using bounds and selective enumeration," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 22, no. 9, pp. 1243–1260, September 2003.

- [4] N. Akhiezer, The Classical Moment Problem and Some Related Questions in Analysis. Oliver and Boyd, 1965.

- [5] C. Amin, N. Menezes, K. Killpack, F. Dartu, U. Choudhury, N. Hakim, and Y. Ismail, "Statistical static timing analysis: how simple can we get?," in *IEEE Design Automation Conference*, pp. 652–657, 2005.

- [6] K. Antreich, H. Graeb, and C. Wieser, "Circuit analysis and optimization driven by worst-case distances," *IEEE Trans. Computer-Aided Design of Inte*grated Circuits and Systems, vol. 13, no. 1, pp. 57–71, January 1994.

- [7] A. Asenov, S. Kaya, and A. Brown, "Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness," *IEEE Trans. Electron Devices*, vol. 50, no. 5, pp. 1254–1260, May 2003.

- [8] P. Avouris, J. Appenzeller, R. Martel, and S. Wind, "Carbon nanotube electronics," *Proceedings of The IEEE*, vol. 91, no. 11, pp. 1772–1784, November 2003.

- [9] D. Bertseksa, Nonlinear Programming. Athena Scientific, 1999.

- [10] S. Bhardwaj, S. Vrudhula, P. Ghanta, and Y. Cao, "Modeling of intra-die process variations for accurate analysis and optimization of nano-scale circuits," in *IEEE Design Automation Conference*, pp. 791–796, 2006.

- [11] D. Boning, J. Panganiban, K. Gonzalez-Valentin, S. Nassif, C. Mcdowell, A. Gattiker, and F. Liu, "Test structures for delay variability," *IEEE International Workshop on Timing Issues in the Specification and Synthesis of Digital Systems*, pp. 109–109, 2002.

- [12] M. Bosley and F. Lees, "A survey of simple transfer-function derivations from high-order state-variable models," *Automatica*, vol. 8, pp. 765–775, 1972.

- [13] S. Boyd and L. Vandenberghe, *Convex Optimization*. Cambridge University Press, 2004.

- [14] J. Carballo and S. Nassif, "Impact of design-manufacturing interface on SoC design methodologies," *IEEE Design and Test of Computers*, vol. 21, no. 3, pp. 183–191, May-June 2004.

- [15] M. Celik, L. Pileggi, and A. Odabasioglu, *IC Interconnect Analysis*. Kluwer Academic Publishers, 2002.

- [16] K. Chan and I. Galton, "A 14b 100MS/s DAC with fully segmented dynamic element matching," in *IEEE International Solid State Circuits Conference*, pp. 2390–2399, 2006.

- [17] H. Chang and S. Sapatnekar, "Full-chip analysis of leakage power under process variations, including spatial correlations," in *IEEE International Confer*ence on Computer Aided Design, pp. 523–528, 2005.

- [18] H. Chang and S. Sapatnekar, "Statistical timing analysis under spatial correlations," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 24, no. 9, pp. 1467–1482, September 2005.

- [19] H. Chang, V. Zolotov, S. Narayan, and C. Visweswariah, "Parameterized block-based statistical timing analysis with non-Gaussian parameters, nonlinear delay functions," in *IEEE Design Automation Conference*, pp. 71–76, 2005.

- [20] L. Chang, Y. Choi, D. Ha, P. Panade, S. Xiong, J. Bokor, C. Hu, and T. King, "Extremely scaled silicon nano-CMOS devices," *Proceedings of The IEEE*, vol. 91, no. 11, pp. 1860–1873, November 2003.

- [21] C. Chen, C. Chu, and D. Wong, "Fast and exact simultaneous gate and wire sizing by Lagrangian relaxation," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, no. 7, pp. 1014–1025, July 1999.

- [22] T. Chen and S. Naffziger, "Comparison of adaptive body bias (ABB) and adaptive supply voltage (ASV) for improving delay and leakage under the presence of process variation," *IEEE Trans. Very Large Scale Integration Systems*, vol. 11, no. 5, pp. 888–899, 2003.

- [23] C. Clark, "The greatest of a finite set of random variables," Operations Research, pp. 145–162, March-April 1961.

- [24] G. Debyser and G. Gielen, "Efficient analog circuit synthesis with simultaneous yield and robustness optimization," in *IEEE International Conference of Computer Aided Design*, pp. 308–311, 1998.

- [25] A. Devgan, "Transient simulation of integrated circuits in the charge-voltage plane," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Sys*tems, vol. 15, no. 11, pp. 1379–1390, November 1996.

#### Full text available at: http://dx.doi.org/10.1561/100000008

- [26] A. Devgan and C. Kashyap, "Block-based static timing analysis with uncertainty," in *IEEE International Conference on Computer Aided Design*, pp. 607–614, 2003.

- [27] A. Devgan and R. Rohrer, "Adaptively controlled explicit simulation," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 13, no. 6, pp. 746–762, June 1994.

- [28] A. Dharchoudhury and S. Kang, "Worst-case analysis and optimization of VLSI circuit performances," *IEEE Trans. Computer-Aided Design of Inte*grated Circuits and Systems, vol. 14, no. 4, pp. 481–492, April 1995.

- [29] S. Director, P. Feldmann, and K. Krishna, "Statistical integrated circuit design," *IEEE Journal of Solid-State Circuits*, vol. 28, no. 3, pp. 193–202, March 1993.

- [30] P. Feldman and S. Director, "Integrated circuit quality optimization using surface integrals," *IEEE Trans. Computer-Aided Design of Integrated Circuits* and Systems, vol. 12, no. 12, pp. 1868–1878, December 1993.

- [31] J. Fishburn and A. Dunlop, "TILOS: a posynomial programming approach to transistor sizing," in *IEEE International Conference on Computer Aided Design*, pp. 326–328, 1985.

- [32] K. Francken and G. Gielen, "A high-level simulation and synthesis environment for ΔΣ modulators," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 22, no. 8, pp. 1049–1061, August 2003.

- [33] J. Friedman and W. Stuetzle, "Projection pursuit regression," Journal of the American Statistical Association, vol. 76, no. 376, pp. 817–823, 1981.

- [34] T. Fukuda, F. Arai, and L. Dong, "Assembly of nanodevices with carbon nanotubes through nanorobotic manipulations," *Proceedings of The IEEE*, vol. 91, no. 11, pp. 1803–1818, November 2003.

- [35] T. Gan, T. Tugbawa, B. Lee, D. Boning, and S. Jang, "Modeling of reverse tone etch back shallow trench isolation chemical mechanical polishing," *Journal of Electrochemical Society*, vol. 148, no. 3, pp. G159–G165, March 2001.

- [36] G. Gielen and R. Rutenbar, "Computer-aided design of analog and mixedsignal integrated circuits," *Proceedings of the IEEE*, vol. 88, no. 12, pp. 1825– 1852, December 2000.

- [37] G. Gielen and W. Sansen, Symbolic Analysis for Automated Design of Analog Integrated Circuits. Springer, 1991.

- [38] G. Golub and C. Loan, *Matrix Computations*. The Johns Hopkins Univ. Press, 1996.

- [39] H. Graeb, S. Zizala, J. Eckmueller, and K. Antreich, "The sizing rules method for analog integrated circuit design," in *IEEE International Conference of Computer Aided Design*, pp. 343–349, 2001.

- [40] K. Heloue and F. Najm, "Statistical timing analysis with two-sided constraints," in *IEEE International Conference on Computer Aided Design*, pp. 828–835, 2005.

- [41] M. Hershenson, "Design of pipeline analog-to-digital converters via geometric programming," in *IEEE International Conference of Computer Aided Design*, pp. 317–324, 2002.

- [42] M. Hershenson, S. Boyd, and T. Lee, "Optimal design of a CMOS Op-Amp via geometric programming," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 20, no. 1, pp. 1–21, January 2001.

- [43] M. Hershenson, A. Hajimiri, S. Mohan, S. Boyd, and T. Lee, "Design and optimization of LC oscillators," *IEEE International Conference of Computer Aided Design*, pp. 65–69, 1999.

- [44] M. Hershenson, S. Mohan, S. Boyd, and T. Lee, "Optimization of inductor circuits via geometric programming," in *IEEE Design Automation Conference*, pp. 994–998, 1999.

- [45] J. Jess, K. Kalafala, S. Naidu, R. Otten, and C. Visweswariah, "Statistical timing for parametric yield prediction of digital integrated circuits," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 25, no. 11, pp. 2376–2392, November 2006.

- [46] R. Kanj, R. Joshi, and S. Nassif, "Mixture importance sampling and its application to the analysis of SRAM designs in the presence of rare failure events," in *IEEE Design Automation Conference*, pp. 69–72, 2006.

- [47] K. Kasamsetty, M. Ketkar, and S. Sapatnekar, "A new class of convex functions for delay modeling and its application to the transistor sizing problem," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 19, no. 7, pp. 779–788, July 2000.

- [48] V. Kheterpal, T. Hersan, V. Rovner, D. Motiani, Y. Takagawa, L. Pileggi, and A. Strojwas, "Design methodology for IC manufacturability based on regular logic-bricks," in *IEEE Design Automation Conference*, pp. 353–358, 2005.

- [49] M. Krasnicki, R. Phelps, J. Hellums, M. McClung, R. Rutenbar, and L. Carley, "ASP: A practical simulation-based methodology for the synthesis of custom analog circuits," in *IEEE International Conference of Computer Aided Design*, pp. 350–357, 2001.

- [50] M. Krasnicki, R. Phelps, R. Rutenbar, and L. Carley, "MAELSTROM: efficient simulation-based synthesis for custom analog cells," in *IEEE Design Automation Conference*, pp. 945–950, 1999.

- [51] X. Li, P. Gopalakrishnan, Y. Xu, and L. Pileggi, "Robust analog/RF circuit design with projection-based posynomial modeling," in *IEEE International Conference on Computer Aided Design*, pp. 855–862, 2004.

- [52] X. Li, P. Gopalakrishnan, Y. Xu, and L. Pileggi, "Robust analog/RF circuit design with projection-based performance modeling," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 26, no. 1, pp. 2–15, January 2007.

- [53] X. Li, J. Le, M. Celik, and L. Pileggi, "Defining statistical sensitivity for timing optimization of logic circuits with large-scale process and environmental variations," in *IEEE International Conference on Computer Aided Design*, pp. 844–851, 2005.

- [54] X. Li, J. Le, P. Gopalakrishnan, and L. Pileggi, "Asymptotic probability extraction for non-Normal distributions of circuit performance," in *IEEE International Conference on Computer Aided Design*, pp. 2–9, 2004.

- [55] X. Li, J. Le, P. Gopalakrishnan, and L. Pileggi, "Asymptotic probability extraction for nonnormal performance distributions," *IEEE Trans. Computer*-

Aided Design of Integrated Circuits and Systems, vol. 26, no. 1, pp. 16–37, January 2007.

- [56] X. Li, J. Le, and L. Pileggi, "Projection-based statistical analysis of full-chip leakage power with non-log-Normal distributions," in *IEEE Design Automation Conference*, pp. 103–108, 2006.

- [57] X. Li, J. Le, L. Pileggi, and A. Strojwas, "Projection-based performance modeling for inter/intra-die variations," in *IEEE International Conference* on Computer Aided Design, pp. 721–727, 2005.

- [58] X. Li and L. Pileggi, "Efficient parametric yield extraction for multiple correlated non-Normal performance distributions of analog/RF circuits," in *IEEE Design Automation Conference*, pp. 928–933, 2007.

- [59] X. Li, J. Wang, L. Pileggi, T. Chen, and W. Chiang, "Performance-centering optimization for system-level analog design exploration," in *IEEE International Conference on Computer Aided Design*, pp. 422–429, 2005.

- [60] K. Low and S. Director, "An efficient methodology for building macromodels of IC fabrication processes," *IEEE Trans. Computer-Aided Design of Inte*grated Circuits and Systems, vol. 8, no. 12, pp. 1299–1313, December 1989.

- [61] W. Maly, H. Heineken, J. Khare, and P. Nag, "Design for manufacturability in submicron domain," in *IEEE International Conference on Computer Aided Design*, pp. 690–697, 1996.

- [62] P. Mandal and V. Visvanathan, "CMOS Op-Amp sizing using a geometric programming formulation," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 20, no. 1, pp. 22–38, January 2001.

- [63] M. Mani, A. Singh, and M. Orshansky, "Joint design-time and post-silicon minimization of parametric yield loss using adjustable robust optimization," in *IEEE International Conference on Computer Aided Design*, pp. 19–26, 2006.

- [64] M. Mckay, R. Beckman, and W. Conover, "A comparison of three methods for selecting values of input variables in the analysis of output from a computer code," *Technometrics*, vol. 21, no. 2, pp. 239–245, May 1979.

- [65] C. Michael and M. Ismail, "Statistical modeling of device mismatch for analog MOS integrated circuits," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 2, pp. 154–166, February 1992.

- [66] D. Montgomery, Design and Analysis of Experiments. Wiley & Sons, 2004.

- [67] T. Mukherjee, L. Carley, and R. Rutenbar, "Efficient handling of operating range and manufacturing line variations in analog cell synthesis," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 19, no. 8, pp. 825–839, August 2000.

- [68] S. Mukhopadhyay, A. Raychowdhury, and K. Roy, "Accurate estimation of total leakage in nanometer-scale bulk CMOS circuits based on device geometry and doping profile," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 24, no. 3, pp. 363–381, March 2005.

- [69] R. Myers and D. Montgomery, Response Surface Methodology: Process and Product Optimization Using Designed Experiments. Wiley-Interscience, 2002.

- [70] F. Najm and N. Menezes, "Statistical timing analysis based on a timing yield model," in *IEEE Design Automation Conference*, pp. 460–465, 2004.

- [71] A. Nardi, A. Neviani, E. Zanoni, M. Quarantelli, and C. Guardiani, "Impact of unrealistic worst case modeling on the performance of VLSI circuits in deep submicron CMOS technologies," *IEEE Trans. Semiconductor Manufacturing*, vol. 12, no. 4, pp. 396–402, November 1999.

- [72] S. Nassif, "Delay variability: sources, impacts and trends," in *IEEE Interna*tional Solid-State Circuits Conference, pp. 368–369, 2000.

- [73] S. Nassif, "Modeling and analysis of manufacturing variations," in *IEEE Cus*tom Integrated Circuits Conference, pp. 223–228, 2001.

- [74] W. Nye, D. Riley, A. Sangiovanni-Vincentelli, and A. Tits, "DELIGHT.SPICE: an optimization-based system for the design of integrated circuits," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 7, no. 4, pp. 501–519, April 1988.

- [75] S. Ohkawa, M. Aoki, and H. Masuda, "Analysis and characterization of device variations in an LSI chip using an integrated device matrix array," *IEEE Trans. Semiconductor Manufacturing*, vol. 17, no. 2, pp. 155–165, May 2004.

- [76] M. Orshansky and A. Bandyopadhyay, "Fast statistical timing analyssi handling arbitrary delay correlations," in *IEEE Design Automation Conference*, pp. 337–342, 2004.

- [77] M. Orshansky, J. Chen, and C. Hu, "Direct sampling methodology for statistical analysis of scaled CMOS technologies," *IEEE Trans. Semiconductor Manufacturing*, vol. 12, no. 4, pp. 403–408, November 1999.

- [78] M. Orshansky and K. Keutzer, "A general probabilistic framework for worst case timing analysis," in *IEEE Design Automation Conference*, pp. 556–561, 2002.

- [79] M. Orshansky, L. Milor, P. Chen, K. Keutzer, and C. Hu, "Impact of spatial intrachip gate length variability on the performance of high-speed digital circuits," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 21, no. 5, pp. 544–553, May 2002.

- [80] M. Orshansky, L. Milor, and C. Hu, "Characterization of spatial intrafield gate CD variability, its impact on circuit performance, and spatial masklevel correction," *IEEE Trans. Semiconductor Manufacturing*, vol. 17, no. 1, pp. 2–11, February 2004.

- [81] A. Papoulis and S. Pillai, Probability, Random Variables and Stochastic Processes. McGraw-Hill, 2001.

- [82] T. Park, T. Tugbawa, J. Yoon, D. Boning, J. Chung, R. Muralidhar, S. Hymes, Y. Gotkis, S. Alamgir, R. Walesa, L. Shumway, G. Wu, F. Zhang, R. Kistler, and J. Hawkins, "Pattern and process dependencies in copper damascene chemical mechanical polishing processes," in *VLSI Multilevel Interconnect Conference*, pp. 437–442, 1998.

- [83] E. Pebesma and G. Heuvelink, "Latin hypercube sampling of Gaussian random fields," *Technometrics*, vol. 41, no. 4, pp. 303–312, November 1999.

- [84] J. Pelgrom, C. Duinmaijer, and P. Welbers, "Matching properties of MOS transistors," *IEEE Journal of Solid-State Circuits*, vol. 25, no. 5, pp. 1433– 1439, October 1989.

- [85] R. Phelps, M. Krasnicki, R. Rutenbar, L. Carley, and J. Hellums, "Anaconda: simulation-based synthesis of analog circuits via stochastic pattern

search," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 19, no. 6, pp. 703–717, June 2000.

- [86] L. Pileggi, H. Schmit, A. Strojwas, P. Gopalakrishnan, V. Kheterpal, A. Koorapaty, C. Patel, V. Rovner, and K. Tong, "Exploring regular fabrics to optimize the performance-cost trade-off," in *IEEE Design Automation Conference*, pp. 782–787, 2003.

- [87] L. Pillage and R. Rohrer, "Asymptotic waveform evaluation for timing analysis," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 9, no. 4, pp. 352–366, April 1990.

- [88] G. Plas, G. Debyser, F. Leyn, K. Lampaert, J. Vandenbussche, W. S. G. Gielen, P. Veselinovic, and D. Leenaerts, "AMGIE a synthesis environment for CMOS analog integrated circuits," *IEEE Trans. Computer-Aided Design* of *Integrated Circuits and Systems*, vol. 20, no. 9, pp. 1037–1058, September 2001.

- [89] R. Rao, A. Devgan, D. Blaauw, and D. Sylvester, "Parametric yield estimation considering leakage variability," in *IEEE Design Automation Conference*, pp. 442–447, 2004.

- [90] S. Ray and B. Song, "A 13b linear 40MS/s pipelined ADC with self-configured capacitor matching," in *IEEE International Solid State Circuits Conference*, pp. 852–861, 2006.

- [91] B. Razavi, Design of Analog CMOS Integrated Circuits. McGraw, 2001.

- [92] C. Robert and G. Casella, Monte Carlo Statistical Methods. Springer, 2005.

- [93] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," *Proceedings of The IEEE*, vol. 91, no. 2, pp. 305–327, February 2003.

- [94] B. Rubinstein, Simulation and the Monte Carlo Method. Wiley & Sons, 1981.

- [95] S. Sapatnekar, *Timing.* Springer, 2004.

- [96] S. Sapatnekar, V. Rao, P. Vaidya, and S. Kang, "An exact solution to the transistor sizing problem for CMOS circuits using convex optimization," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 12, no. 11, pp. 1621–1634, November 1993.

- [97] F. Schenkel, M. Pronath, S. Zizala, R. Schwencker, H. Graeb, and K. Antreich, "Mismatch analysis and direct yield optimization by spec-wise linearization and feasibility-guided search," in *IEEE Design Automation Conference*, pp. 858–863, 2001.

- [98] G. Seber, *Multivariate Observations*. Wiley Series, 1984.

- [99] A. Seifi, K. Ponnambalam, and J. Vlach, "A unified approach to statistical design centering of integrated circuits with correlated parameters," *IEEE Trans. Circuits and Systems – I*, vol. 46, no. 1, pp. 190–196, January 1999.

- [100] Semiconductor Industry Associate, International Technology Roadmap for Semiconductors. 2005.

- [101] M. Sengupta, S. Saxena, L. Daldoss, G. Kramer, S. Minehane, and J. Chen, "Application-specific worst case corners using response surfaces and statistical models," *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 24, no. 9, pp. 1372–1380, September 2005.

- 150 References

- [102] B. Silverman, Density Estimation for Statistics and Data Analysis. Chapman & Hall/CRC, 1986.

- [103] B. Simon, "The classical moment problem as a self-adjoint finite difference operator," Advances in Mathematics, vol. 137, no. 1, pp. 82–203, July 1998.

- [104] K. Singhal and V. Visvanathan, "Statistical device models from worst case files and electrical test data," *IEEE Trans. Semiconductor Manufacturing*, vol. 12, no. 4, pp. 470–484, November 1999.

- [105] A. Singhee and R. Rutenbar, "From finance to flip flops: A study of fast quasi-Monte Carlo methods from computational finance applied to statistical circuit analysis," in *IEEE International Symposium on Quality Electronic Design*, 2007.

- [106] A. Srivastava, S. Shah, K. Agarwal, D. Sylvester, D. Blaauw, and S. Director, "Accurate and efficient gate-level parametric yield estimation considering correlated variations in leakage power and performance," in *IEEE Design Automation Conference*, pp. 535–540, 2005.

- [107] G. Stehr, M. Pronath, F. Schenkel, H. Graeb, and K. Antreich, "Initial sizing of analog integrated circuits by centering within topology-given implicit specifications," in *IEEE International Conference of Computer Aided Design*, pp. 241–246, 2003.

- [108] B. Stine, D. Boning, and J. Chung, "Inter- and intra-die polysilicon critical dimension variation," SPIE Symposium on Microelectronic Manufacturing, pp. 27–36, 1996.

- [109] B. Stine, D. Boning, and J. Chung, "Analysis and decomposition of spatial variation in integrated circuit processes and devices," *IEEE Trans. Semiconductor Manufacturing*, vol. 10, no. 1, pp. 24–41, February 1997.

- [110] B. Stine, D. Ouma, R. Divecha, D. Boning, J. Chung, D. Hetherington, I. Ali, G. Shinn, J. Clark, O. Nakagawa, and S. Oh, "A closed form expression for ILD thickness variation in CMP processes," in *CMP-MIC Conference*, pp. 266–273, 1997.

- [111] P. Stolk, F. Widdershoven, and D. Klaassen, "Modeling statistical dopant fluctuations in MOS transistors," *IEEE Trans. Electron Devices*, vol. 45, no. 9, pp. 1960–1971, September 1998.

- [112] J. Tschanz, J. Kao, S. Narendra, R. Nair, D. Antoniadis, A. Chandrakasan, and V. De, "Adaptive body bias for reducing impacts of die-to-die and within-die parameter variations on microprocessor frequency and leakage," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 11, pp. 1396–1402, November 2002.

- [113] S. Tsukiyama, M. Tanaka, and M. Fukui, "A statistical static timing analysis considering correlations between delays," in *IEEE Asia and South Pacific Design automation Conference*, pp. 353–358, 2001.

- [114] J. Vanderhaegen and R. Brodersen, "Automated design of operational transconductance amplifiers using reversed geometric programming," in *IEEE Design Automation Conference*, pp. 133–138, 2004.

- [115] C. Visweswariah, K. Ravindran, K. Kalafala, S. Walker, S. Narayan, D. Beece, J. Piaget, N. Venkateswaran, and J. Hemmett, "First-order incremental block-based statistical timing analysis," *IEEE Trans. Computer-Aided Design*

of Integrated Circuits and Systems, vol. 25, no. 10, pp. 2170–2180, October 2006.

- [116] Z. Wang and S. Director, "An efficient yield optimization method using a two step linear approximation of circuit performance," in *IEEE European Design* and Test Conference, pp. 567–571, 1994.

- [117] J. Wojciechowski and J. Vlach, "Ellipsoidal method for design centering and yield estimation," *IEEE Trans. Computer-Aided Design of Integrated Circuits* and Systems, vol. 12, no. 10, pp. 1570–1579, October 1993.

- [118] A. Wong, R. Ferguson, and S. Mansfield, "The mask error factor in optical lithography," *IEEE Trans. Semiconductor Manufacturing*, vol. 13, no. 2, pp. 235–242, May 2000.

- [119] J. Xiong, V. Zolotov, and L. He, "Robust extraction of spatial correlation," *IEEE International Symposium on Physical Design*, pp. 2–9, 2006.

- [120] J. Xiong, V. Zolotov, N. Venkateswaran, and C. Visweswariah, "Criticality computation in parameterized statistical timing," in *IEEE Design Automation Conference*, pp. 63–68, 2005.

- [121] Y. Xu, C. Boone, and L. Pileggi, "Metal-mask configurable RF front-end circuits," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 8, pp. 1347–1351, August 2004.

- [122] Y. Xu, K. Hsiung, X. Li, I. Nausieda, S. Boyd, and L. Pileggi, "OPERA: optimization with ellipsoidal uncertainty for robust analog IC design," in *IEEE Design Automation Conference*, pp. 632–637, 2005.

- [123] Y. Xu, L. Pileggi, and S. Boyd, "ORACLE: optimization with recourse of analog circuits including layout extraction," in *IEEE Design Automation Conference*, pp. 151–154, 2004.

- [124] Y. Zhan, A. Strojwas, X. Li, L. Pileggi, D. Newmark, and M. Sharma, "Correlation aware statistical timing analysis with non-Gaussian delay distributions," in *IEEE Design Automation Conference*, pp. 77–82, 2005.

- [125] L. Zhang, W. Chen, Y. Hu, J.Gubner, and C. Chen, "Correlation-preserved non-Gaussian statistical timing analysis with quadratic timing model," in *IEEE Design Automation Conference*, pp. 83–88, 2005.